CPU缓存策略原理

缓存概述

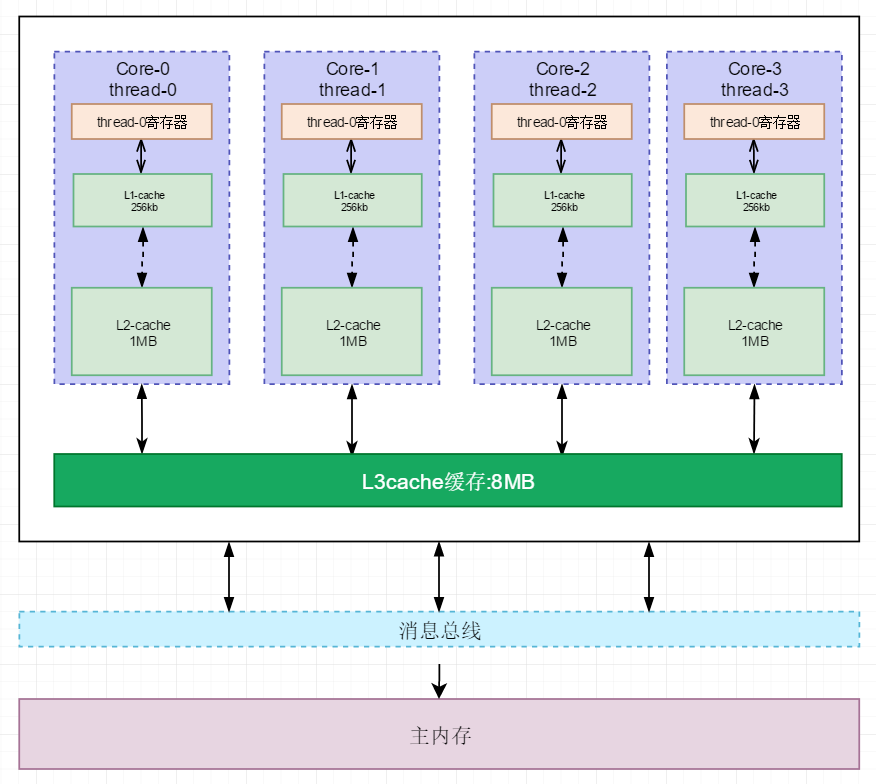

CPU为了提升执行效率,减少CPU与内存的交互(交互影响CPU效率),一般在CPU上集成了多级缓存架构

cpu缓存策略图

cpu读取数据时, 会先从自己的寄存器当中读取.如果没有再从Cache当中读取数据.如果Cache当中也没能.再从内存当中获取.然后再依次缓存

多核CPU结构图

三级缓存

L1 Cache

分为数据缓存和指令缓存,逻辑核独占

CPU所有操作的数据全部在寄存器当中完成

寄存器比L1要快

离CPU内核最近

内核独享

L1一种存指令,一种存数据

L2 Cache

内核独享

L3 Cache

所有内核共享

缓存读取时间

Registers(寄存器组) `<1ns`

L1 cache (一级缓存) `约1ns`

L2 cache(二级缓存) `约3ns`

L3cache(三级缓存) `约15ns`

主内存(最终存储地址) `约80ns`

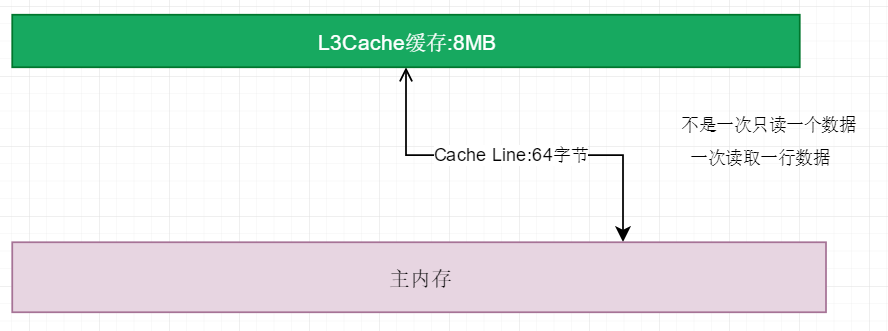

缓存行Cache Line概念

1. 缓存是由最小的存储区块缓存行Cache Line组成

2. 计算机当中为了让效率更高,在读取数据时,是一块一块进行读取的

3. cache Line能够读取的大小是64个字节

cpu缓存一致性问题

假设cpu1从主内存当中读取一个共享数据i = 1,读取到cache当中 进行数据的修改,把i修改为2

一、同时同一个cpu也从内存当中读取数据

- 此时读取的结构可能是1也可能是2

- 如果cpu1把写的结果写到到内存中, cpu2读取的就是2

- 如果cpu1没有把结果写回到主内存当中,cpu2读取的就是1

cpu缓存一致性解决方案

1.总线加锁

cpu1在读取的时候不允许其它cpu进行读取

弊端: 降低了cpu的吞吐量

2.缓存上的一致性协议MESI

后续再说MESI先有个印象

程序的局部性原理

问题

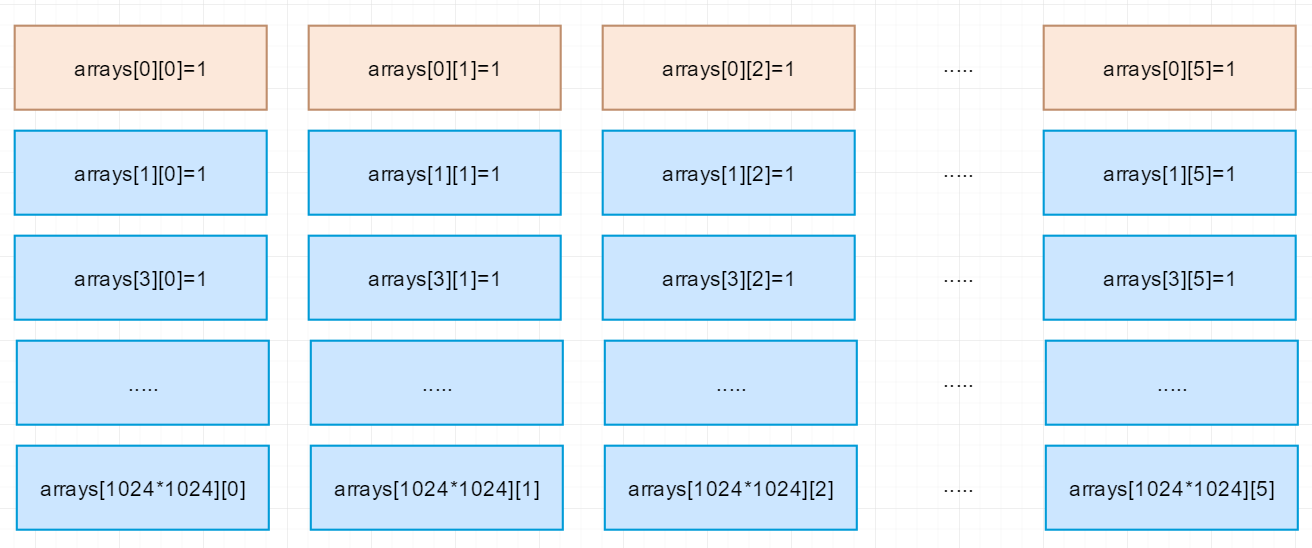

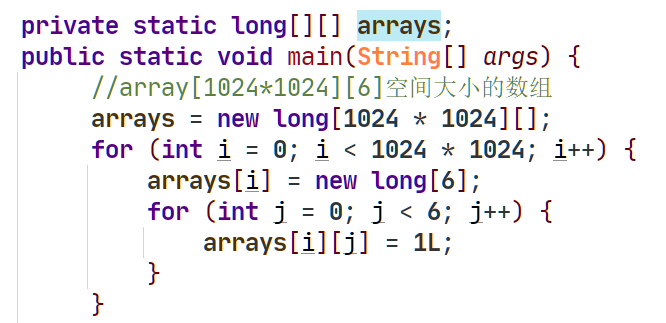

构建数组

创建一个大的二维数组

任务:两种方式所有元素进行求和

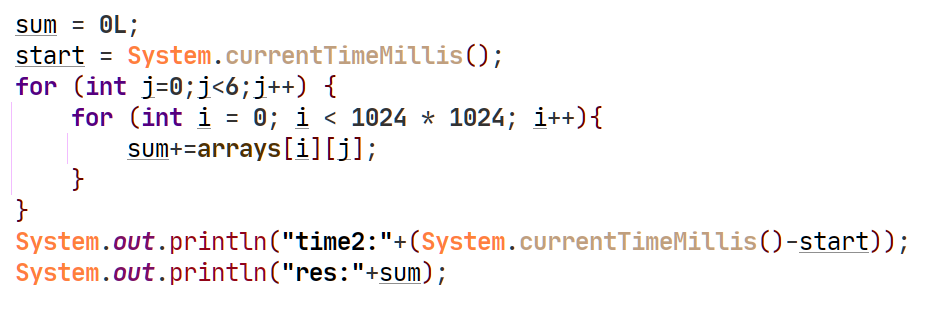

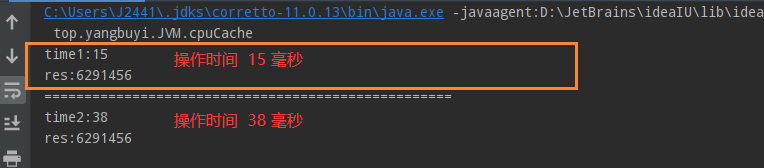

请自行根据图片将代码执行查看效果

思考问题

为什么会产生这么多时间呢? 如何进行读取的呢?

分析原理

上面一种连续按行读取

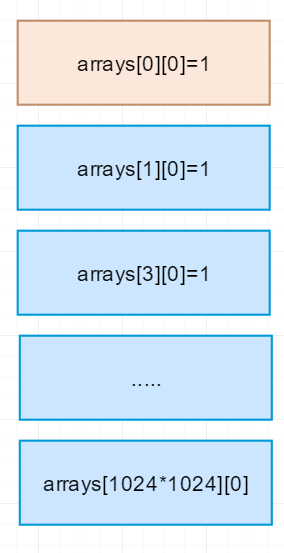

下面一种是按列读取

经过上面的问题牵扯出一个叫局部性原理的问题

一、什么是局部性原理

- 在CPU访问寄存器时,无论是存取数据抑或存取指令,都趋于聚集在一片连续的区域中,这就被称为局部性原理

- 当读到某一个数据的时候,可能很快就会用到和它相邻的值,此时就会把它相邻的值也一起读取,来提高程序的效率

- 局部性原理有些像概率问题,被使用过的数据:在时间上,大概率会被多次使用;在空间上,其附近的位置“大概率”也会被引用

空间局部性

如果一个存储器的位置被引用,那么将来他附近的位置也会被引用

时间局部性

被引用过一次的存储器位置在未来会被多次引用那么在近期它很可能还会被再次访问

评论区